Six Named to National Academy of Inventors

Dec 12, 2023 — Atlanta, GA

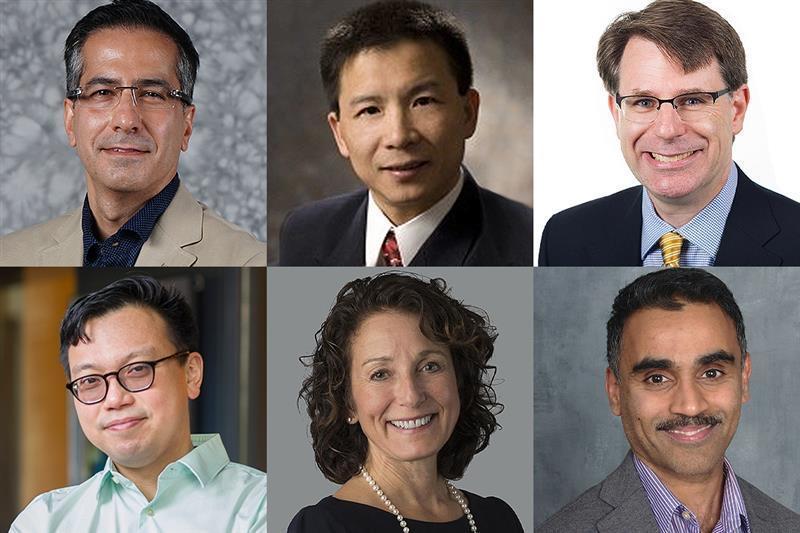

Six Georgia Tech College of Engineering faculty members are among the National Academy of Inventors (NAI) 2023 Class of Fellows. The honor is the highest professional distinction awarded solely to inventors.

No other university or organization in the world has more honorees this year than Georgia Tech. The group of six holds more than 200 patents.

- Farrokh Ayazi, electrical and computer engineering

- Maohong Fan, civil and environmental engineering

- Christopher Jones, chemical and biomolecular engineering

- Wilbur Lam, biomedical engineering

- Susan Margulies, biomedical engineering

- Karthikeyan Sundaresan, electrical and computer engineering

The Georgia Tech engineers are among 162 worldwide inventors honored in 2023. According to the NAI, “their work spans across disciplines and exemplifies their dedication and inspiration to translating research into commercial technologies that benefit society.”

The 2023 class will be honored in June at the NAI annual meeting.

Jason Maderer, College of Engineering Director of Communications

jason.maderer@coe.gatech.edu

Georgia Tech and Samsung Look to Unleash the Future of Digital Storage

Dec 11, 2023 —

The rise of artificial intelligent (AI)-driven marvels hinges on cutting-edge data storage solutions. Without efficient data storage, applications like self-driving cars, life-saving healthcare diagnostics, and responsive voice assistants would fall short of their true potential.

At the forefront of this evolving data storage landscape, a collaboration between the Georgia Institute of Technology and Samsung seeks to substantially decrease the voltage in existing technology, unlocking the full potential of AI systems.

“Finding innovative solutions in data storage is paramount, it’s not just about saving photos or documents anymore. The storage needed is about enabling AI systems to transform how we interact with our devices, the world around us, and even each other,” said Asif Khan, an assistant professor in the School of Electrical and Computer Engineering (ECE) with a joint appointment in the School of Materials Science and Engineering (MSE).

Khan's lab is spearheading the collaboration which brings together three ECE labs, including those of Professors Suman Datta and Shimeng Yu. The lead author of the paper is Dipjyoti Das, a postdoctoral fellow under Khan's supervision. The second author, Hyeonwoo Park, conducts research under Datta. The team is joined by researchers from MSE, the Institute of Materials, the Institute of Electronics and Nanotechnology, and a dedicated team from Samsung.

“This is a pivotal era of transformation and opportunity in high-memory compute,” said co-author Suhwan Lim, an engineer at Samsung. “Strategic intersectoral relationships like this between Samsung and Georgia Tech nurture innovative thinking and lead to exciting experiential results that push us all forward.”

Adding to the already substantial Georgia Tech presence in the field of computer memory storage, the team's findings will be featured at the upcoming International Electron Devices Meeting (IEDM) in San Francisco this month.

The Quest for Voltage Efficiency

The research focuses on improving NAND flash technology found at the core of storage devices like solid-state hard drives, USB sticks, and SD cards. NAND boasts an impressive 1,000-layer 3D architecture, cramming 100 terabytes of data into a minuscule space.

However, the critical challenge is NAND’s persistent high voltage requirements. Exceeding 20 volts poses challenges in computing due to increased energy consumption, heat generation, and the risk of damaging electronic components.

“NAND has been the backbone of data storage, so our research doesn't attempt to replace it; it's an upgrade. We're boosting NAND's power and pushing it into the digital storage future,” said Das, who designed and executed experiments, as well as contributed to characterization.

A Ferroelectric Future

The paper’s groundbreaking proposal aims to revolutionize NAND flash technology by replacing the traditional NAND gate stack — a multi-layered structure in a transistor essential for controlling the flow of electrical current in semiconductor devices — with a new ferroelectric structure and a tunneling barrier.

The team's method, introducing aluminum oxide (Al2O3) in the middle of the ferroelectric stack, has dramatically improved data storage capability, reducing voltage requirements by an impressive 40-60%.

Additionally, the study reveals that the Al2O3 layer functions as a tunnel barrier, impeding electron motion and establishing a dipole, creating an additional electric field that aligns with the polarization direction, boosting device memory performance.

The experiential findings could transform various sectors, including AI, mobile devices, edge data processing, embedded systems, and overall computing efficiency.

“This breakthrough charts a new course towards more efficient, reliable and dense data storage solution,” said Datta, who is the Joseph M. Pettit Chair of Advanced Computing in ECE and a Georgia Research Alliance (GRA) Eminent Scholar. “We are grateful to Samsung for their continued support, as we work towards the next milestone.”

Looking for Collective Solutions to Shared Challenges

According to Das, the approach not only demonstrates the capability to achieve reduced voltage and enhanced memory but also aligns with scalability and broad industry adoption.

As the project ventures into commercial avenues, the input of Samsung's researchers will be crucial. Das and Park are actively uncovering the intricacies of disturbances that could impede the market acceptance of the new gate stack.

In this context, disturbances refer to any unintended disruptions or deviations from transistor behavior expectations. Das stresses the importance of understanding, controlling, and clearly defining disturbance specifications. Establishing a well-defined threshold for disturbances is pivotal for achieving widespread commercialization readiness in their research.

“Working alongside industry leaders like Samsung is essential for any endeavor aiming to make a transformative impact in everyday technology,” added Khan. “It becomes particularly pertinent as we collectively look towards a future dominated by the power required to fuel advancements in AI.”

Citation: Dipjyoti Das*, Hyeonwoo Park*, Zekai Wang, Chengyang Zhang, Prasanna Venkatesan Ravindran, Chinsung Park, Nashrah Afroze, Po-Kai Hsu, Mengkun Tian, Hang Chen, Winston Chern, Suhwan Lim, Kwangsoo Kim, Kijoon Kim, Wanki Kim, Daewon Ha; Shimeng Yu, Suman Datta, Asif Khan. “Experimental Demonstration and Modeling of a Ferroelectric Gate Stack with a Tunnel Dielectric Insert for NAND Applications.” Proceedings of the 2023 IEEE International Electron Devices Meeting (IEDM). Paper # 24.1

Dan Watson

New IEN Center to Research Wearable Technologies

Dec 05, 2023 —

A new research center in the Institute for Electronics and Nanotechnology (IEN) will help bring together human-centered bioelectronics technology research to improve human healthcare and expand human-machine interface technologies.

The Wearable Intelligent Systems and Healthcare (WISH) Center will work to push innovation in wearable sensors and electronics technologies. Focus areas of the center will include electronics, artificial intelligence, biological science, material sciences, manufacturing, system design, and medical engineering.

“We are excited by the promise of bioelectronics improving human health and all the exciting science engineering that is required to make it a reality,” said Michael Filler, interim executive director of IEN.

WISH is directed by W. Hong Yeo, associate professor in Georgia Tech’s George W. Woodruff School of Mechanical Engineering and the Wallace H. Coulter Department of Biomedical Engineering at Georgia Tech and Emory, and Yuhang Hu, associate professor in the School of Chemical and Biomolecular Engineering at Georgia Tech.

“I founded WISH to bring together Georgia Tech’s expertise in various disciplines and to create opportunities for developing wearable bioelectronics and human-machine technologies leading to better lives and communities,” said Yeo.

Yeo’s research focuses on developing soft sensors, electronics and robotics for health monitoring and disease diagnosis at the intersection of human and machine interaction. Other researchers in the center represent disciplines from across Georgia Tech’s Colleges of Engineering, Computing, Sciences, Design, and Liberal Arts; Emory University; and Children’s Healthcare of Atlanta.

WISH will be one of IEN’s 10 strategic research centers, along with the 3D Systems Packaging Research Center, a graduated NSF Engineering Research Center focusing on advanced packaging using 2.5D and 3D heterogeneous integration technologies, and the Georgia Electronic Design Center, one of the world’s largest university-based semiconductor research centers. WISH is an evolution of the Center for Human-Centric Interfaces and Engineering, which received seed funding from IEN to focus on collaborative research for human-centered design, biofeedback control, and integrated nanosystems to advance human-machine interaction in the scope of healthcare.

IEN supports early-stage research in underfunded research areas that span all disciplines in science and engineering through its seed grant programs, which focus on research in biomedicine, electronics, optoelectronics and photonics, and energy applications.

Amelia Neumeister, Research Communications

Andreas Heirlemann Gives Inaugural Oliver Brand Memorial Lecture on Electronics and Nanotechnology

Dec 04, 2023 —

The inaugural Oliver Brand Memorial Lectureship on Electronics and Nanotechnology was held on Nov. 13 at Georgia Tech. The lecture was presented by Andreas Heirlemann, professor of biosystems science and engineering at ETH Zürich, on microphysicological systems and highly integrated microelectrode arrays.

His talk marks the beginning of an annual lecture series established in memory of Professor Oliver Brand, who passed away in April. Brand had served as the executive director of the Georgia Tech Institute for Electronics and Nanotechnology (IEN) since 2014.

“Oliver’s work, especially in microelectromechanical systems and CMOS-based microsystems, is widely respected in the community, with more than 190 publications to his name,” said Mike Filler, IEN’s interim executive director. “Andreas Heirlemann’s scientific contributions embody the innovative spirit and excellence that Oliver championed throughout his life.”

In addition to their research connection, Heirlemann also had a personal connection with Brand. They worked closely together in the same research lab at ETH Zürich for three years before Brand moved to Georgia Tech.

“What impressed me most about Oliver was his innate friendliness,” said Hierlemann. “He was always supportive. He was always motivating students. I never heard a harsh word come out of him. He had an extremely positive outlook on life that I learned to admire. That is what I take as his legacy.”

Hierlemann’s lecture was presented in two parts. The first focused on microfluidics, hanging drop networks, and microphysiological systems. Microphysicological systems are 3D cell assemblies, or membrane structures like organs, that occur naturally in the body or are grown with stem cells. These systems allow for comprehensive testing and studying tissue interactions.

The second part of his talk focused on high-density microelectrode array systems, including neuronal systems characterization and the handling and use of neurons.

Brand spent more than 20 years as a member of the Georgia Tech faculty. In addition to leading IEN, he was a professor in the School of Electrical and Computer Engineering, director of the Coordinating Office for the NSF-funded National Nanotechnology Coordinated Infrastructure (NNCI), and director of the Southeastern Nanotechnology Infrastructure Corridor, one of the 16 NNCI sites.

Brand united researchers in the fields of electronics and nanotechnology, fostering collaboration and expanding IEN to include more than 200 faculty members. In addition to his respected work in the field of microelectromechanical systems, he is remembered for his kindness, dedication, and unwavering support toward all who knew him.

Amelia Neumeister

amelia.neumeister@research.gatech.edu

2024 NNCI Etch Symposium | Advances in Micro- & Nanoscale Patterning of Strategic and Emerging Materials for Electronic, Photonic, Quantum, & MEMS Devices

We extend a warm invitation to you and your organization to participate in the NNCI Etch Symposium at Georgia Tech. This event, scheduled for April 24-26, 2024, is organized by the National Nanotechnology Coordinated Infrastructure (NNCI), a network supported by the National Science Foundation (NSF).

About NNCI

The Next Generations of Lateral Flow Assays: Integration of Nanomaterials

About the Speaker

Fall 2023 IEN Seed Grant Winners Announced

Nov 30, 2023 —

The Institute for Electronics and Nanotechnology (IEN) at Georgia Tech has announced the Fall 2023 Core Facility Seed Grant winners. The primary purpose of this program is to give early-stage graduate students in diverse disciplines working on original and unfunded research in micro- and nanoscale projects the opportunity to access the most advanced academic cleanroom space in the Southeast. In addition to accessing the labs' high-level fabrication, lithography, and characterization tools, the awardees will have the opportunity to gain proficiency in cleanroom and tool methodology and access the consultation services provided by research staff members in IEN. Seed Grant awardees are also provided travel support to present their research at a scientific conference.

In addition to student research skill development, this biannual grant program gives faculty with novel research topics the ability to develop preliminary data to pursue follow-up funding sources. The Core Facility Seed Grant program is supported by the Southeastern Nanotechnology Infrastructure Corridor (SENIC), a member of the National Science Foundation’s National Nanotechnology Coordinated Infrastructure (NNCI).

Since the start of the grant program in 2014, 90 projects from ten different schools in Georgia Tech’s Colleges of Engineering and Science, as well as the Georgia Tech Research Institute and three other universities, have been seeded.

The four winning projects in this round were awarded IEN cleanroom and lab access time to be used over the next year. In keeping with the interdisciplinary mission of IEN, the projects that will be enabled by the grants include research in electronic devices, geochemistry, bio-inspired design, and solid state physics.

The Fall 2023 IEN Core Facility Seed Grant Award winners are:

Using Zircon (U-Th)/Pb Geochronology to Trace the Source of Himalayan Megafloods

PI: Karl Lang

Student: Srinanda Nath

School of Earth and Atmospheric Sciences

Material Characterization of Keratin-based Barbules with Hygroscopic Coiling-uncoiling Behaviors and Biomimetic Fabrication of Artificial Hygromorphic Barbules

PI: Saad Bhamla

Student: Nami Ha (ME/BioE)

School of Chemical and Biomolecular Engineering

Ultra-high Mobility Semiconducting Graphene Device Fabrication

PI: Claire Berger and Walt de Heer

Student: Will Griffin

School of Physics

Extracting the Effect of Electrode-Ferroelectric Interface on Photovoltaic Efficiency

PI: Lauren Garten

Student: Marshall Frye

School of Materials Science and Engineering

The Southeastern Nanotechnology Infrastructure Corridor, a member of the National Nanotechnology Coordinated Infrastructure, is funded by NSF Grant ECCS-2025462.

Amelia Neumeister

Semiconductor Company Falcomm Raises $4M in Seed Funding to Advance Ultra-Efficient Power Amplifiers, Hires Industry Leaders

Nov 29, 2023 —

Edgar Garay is CEO and founder of Falcomm.

Squadra Ventures led the round with participation from Cambium Capital, Draper Cygnus, and the Georgia Tech Foundation.

Falcomm is built on breakthroughs made over six years in the lab of founder and CEO Edgar Garay to revolutionize the power amplifier, a semiconductor found in devices from satellites to IoT to cellphones, that conditions and blasts the 1s and 0s from software through an antenna. Falcomm’s Dual-Drive PA combines ultra-efficient performance with an architecture that lends itself to production at scale.

“Power amplifiers are the workhorse of the modern electronic era, but improvement to this technology hasn’t kept pace with the rise of the innovation economy,” said Garay, who holds a doctorate in electrical engineering from Georgia Tech’s School of Electrical and Computer Engineering, where he conducted the research that led to the formation of his startup.

“Falcomm’s ultra-efficient, silicon-proven technology will bring advances in power and efficiency to the semiconductor industry that help communications manufacturers to realize massive efficiency gains, while lowering costs. With urgent challenges in the environment and supply chain, we can’t wait another 90 years for change.”

With simultaneous transmission at each terminal of a transistor, the Dual-Drive PA delivers performance that is 1.8 times more efficient at 2 times higher power, with half of the silicon area requirements of traditional power amplifiers. For manufacturers, these gains will reduce thermal management and energy costs, while easing overall system requirements.

A patented architectural design allows the product to be manufactured in high volume by semiconductor foundries in the United States. With fabless technology, the company is poised to grow a network of industry partners that catalyzes expansion in the $23 billion power amplifier market.

Born in Venezuela, Garay developed a passion for using science and engineering to solve problems while repairing machinery on a farm in his hometown. While pursuing doctoral studies at Georgia Tech, he recognized the opportunity to bring innovation to the power amplifier, which had not changed in decades despite the rapid advance of technology and its critical role in devices.

Garay’s research resulted in multiple patents, spurring him to spin out the technology and create Falcomm through assistance from Georgia Tech resources, including VentureLab and CREATE-X. Falcomm is the first company to receive investment from the Georgia Tech Foundation.

“Georgia Tech is proud to support our academic innovators to help them ensure their inventions have real-world impact,” said Raghupathy Sivakumar, Georgia Tech’s vice president of Commercialization and chief commercialization officer. “The Office of Commercialization is rapidly expanding our programs and initiatives to build out the largest and most robust entrepreneurial ecosystem at any public university. I am happy to say that Falcomm is the recipient of the first equity investment out of our new Research Impact Fund targeted specifically at spinouts based on Georgia Tech intellectual property."

The Falcomm team was recently bolstered by the addition of pioneering industry leaders who have demonstrated a track record of innovation in telecommunications, wireless, and semiconductors:

- Thomas Cameron, Ph.D., chief strategy officer, is a 35-year veteran of technology research and development in the wireless industry. During a 12-year stint at Analog Devices, Cameron served as chief technology officer of the Communications Business Unit and was a leading evangelist for the adoption of 5G connectivity. He held leadership and engineering roles in the RF industry at Bell Northern Research, Nortel, Sirenza Microdevices, and WJ Communications. Cameron has seven patents in wireless technology and has authored numerous papers and technical articles.

- Ned Cahoon, director of Foundry and Customer Relationships, brings more than 20 years of RF business development experience across the mobile and wireless infrastructure industries. He helped to stand up IBM’s $1 billion RF business before joining GlobalFoundries in 2016, where he served as a fellow in the office of the chief technology officer. A senior design and go-to-market leader, Cahoon brings experience building networks across foundries, academia, and technology companies.

For Falcomm, the funding follows quickly on the heels of the company’s selection to the TechCrunch Startup Battlefield 200 in 2023. The company is a graduate of the Berkeley SkyDeck Accelerator and the EvoNexus incubator.

Bringing innovation to the tiny power amplifier can have a massive impact on some of the nation’s most pressing challenges. The energy efficiency gains resulting from an increase in power output come at a time of growing urgency around climate change. The ability to manufacture domestically comes at a time when nearshoring is a priority to address cost and supply chain challenges underscored by the global semiconductor shortage and resulting CHIPS Act.

“Edgar and his team are just as inspiring as they are hard-working. They have shown that it’s possible to assemble the talent and operations to innovate on a foundational technology that hasn’t seen meaningful advances in decades anywhere in the country,” said Guy Filippelli, Squadra Ventures’ managing partner. “By boosting efficiency and manufacturing domestically in the critical semiconductor industry, Falcomm’s innovations will bolster American competitiveness.”

The funding will be used to accelerate go-to-market activities with satellite companies and wireless infrastructure manufacturers, advance the company’s patented technology, and expand the team. Falcomm is actively hiring for roles in operations, engineering, and design. View job openings.

For Falcomm:

Stephen Babcock, stephen@squadra.vc

For Georgia Tech:

Péralte C. Paul

peralte@gatech.edu

404.316.1210

Sensor Fabric, Big Data Could Help End Pressure Injuries for Wheelchair Users

Nov 29, 2023 —

Sundaresan Jayaraman (left) looks at pressure data from fabric sensors he developed with Sungmee Park, who is seated in their prototype wheelchair system. (Photo: Candler Hobbs)

At least half of veterans with spinal cord injuries will develop sores on their skin from the unrelieved pressure of sitting for long periods of time in a wheelchair. It’s a constant worry, because these skin ulcers can greatly limit patients’ mobility.

“Pressure injuries directly impact the veteran’s quality of life, because the medical provider will order the veteran to bed rest for weeks and potentially months,” said Kim House, a physician and medical director of the Spinal Cord Injury Clinic at the Atlanta Veterans Administration Healthcare System. “At every clinic visit, I provide education for pressure injury prevention.”

House could one day have a new tool to offer her patients, thanks to researchers in the Georgia Tech College of Engineering, and wheelchair-bound veterans are just the beginning.

Materials engineers are developing new fabric sensors and a customized wheelchair system that assesses and automatically eases pressure at contact points to prevent injuries from developing in the first place.

“We have three key issues happening: First, continuous pressure. Second, moisture, because when you're sitting in the same spot, you tend to sweat and generate moisture. And third is shear. When you try to move somebody, the skin shears. That perfect combination is what causes pressure injuries,” said Sundaresan Jayaraman, professor in the School of Materials Science and Engineering (MSE). “We believe we have a solution to the perfect storm of pressure, moisture and shear, which means the user’s quality of life is going to get better.”

Joshua Stewart

College of Engineering

Nano@Tech Fall 2023 Series | Development and Clinical Translation of Microtechnologies for Hematologic Applications

Abstract: Hematologic processes are frequently comprised of cellular and biomolecular interactions that are biophysical in nature and may involve blood cells (erythrocytes, leukocytes, and platelets), endothelial cells, soluble factors (coagulation proteins, von Willebrand factor, and cytokines), the hemodynamic environment, or all of the above. These phenomena are often pathologically altered in hematologic diseases but are difficult to study using standard in vitro and in vivo systems.