Configurable Analog Chip Computes with 1,000 Times Less Power than Digital

Mar 02, 2016 — Atlanta, GA

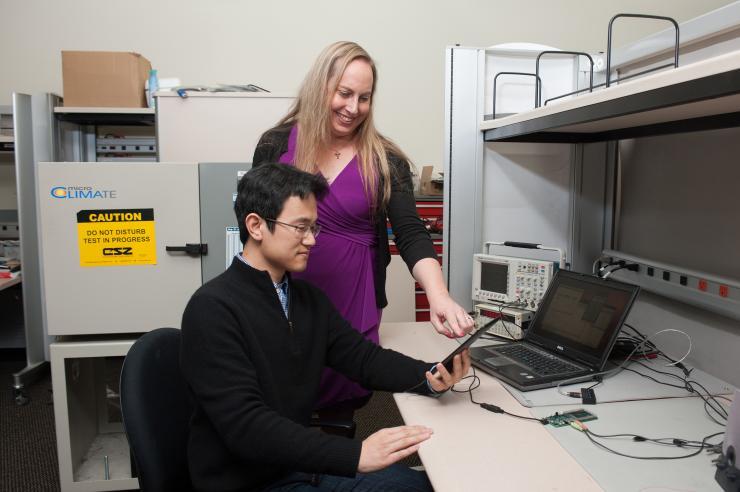

Georgia Tech Graduate Research Assistant Sihwan Kim and Professor Jennifer Hasler are developing an application for the FPAA device. They are using design tools on the laptop computer and evaluating a demonstration on the handheld tablet driving the FPAA device. (Credit: Fitrah Hamid, Georgia Tech)

Researchers have built and demonstrated a novel configurable computing device that uses a thousand times less electrical power – and can be built up to a hundred times smaller – than comparable digital floating-gate configurable devices currently in use.

The new device, called the Field-Programmable Analog Array (FPAA) System-On-Chip (SoC), uses analog technology supported by digital components to achieve unprecedented power and size reductions. The researchers said that for many applications these low-power analog-based chips are likely to work as well as or better than configurable digital arrays.

Currently, field programmable gate arrays (FPGAs) – digital devices widely used in consumer devices, defense systems and more – dominate the configurable chip market. These floating-gate integrated circuits can be altered internally at any time, and techniques to reconfigure them for many different forms and functions are well established.

Professionals familiar with FPGAs will find the programming interface of the new analog chip surprisingly like the digital circuits in many ways, said Jennifer Hasler, a professor in the Georgia Tech School of Electrical and Computer Engineering (ECE) and leader of the research team that produced the new analog architecture.

“But in other ways the FPAA is going to seem quite different,” she said. “In terms of the power needed, it's extremely different because you need only milliwatts to run the analog device, while it’s hard to get an FPGA to work on less than a watt.”

A paper on the new FPAA system-on-chip device has been published on the IEEE Xplore website. Another paper focusing on the details of programming FPAA devices was also published on the Xplore site. In addition a third paper, detailing a high-level open-source programming toolset developed by Hasler and her team for programming analog arrays, has also been published online in the Journal of Low Power Electronics and Applications.

Novel Techniques

Traditionally, analog technology has been used primarily for hard-wired circuits such as sensors that interface between digital devices and the real world; examples include the circuits that detect and reproduce sound in cell phones and other devices. Analog circuits are also used extensively in electronics to regulate and optimize power use. These single-function circuits cannot perform software-based computation, using hardware gates and switches, in the manner of digital integrated circuits.

Hasler’s team, however, has developed techniques that perform computation using an analog-style physical architecture by reliably positioning electrons in an FPAA’s connective structure. This approach stands in contrast to FPGAs, which process electrons through floating gates in ways similar to conventional digital semiconductors such as memory chips or central processing units.

One advantage of FPAAs is that they're non-volatile, Hasler explained, meaning they retain data even when power is turned off. This is similar to flash memory technology, such as the solid-state drives and storage cards commonplace today. The use of non-volatile memory reduces power consumption, in contrast to the higher power needs of the volatile SRAM configurations typically used in FPGAs.

“In addition to being non-volatile, our analog architecture lets us do something fairly radical – we can compute using the routing fabric of the chip, exploiting areas that are usually considered just dead weight,” Hasler said. “To help do this, we've developed highly efficient switches that can be programmed on, off, or in-between – partially on and partially off. This flexibility provides both increased computation capabilities and reduced power consumption.”

Milliwatts or Microwatts

The present FPAA device can operate on less than 30 milliwatts – thousandths of a watt, Hasler explained. That level approaches three orders of magnitude less than a conventional digital configurable chip. Further design advances in analog arrays could bring their power needs down into the microwatt range – millionths of a watt.

To program the analog environment of the new device, researchers manipulate electrons in precise ways. Using electron-injection and electron-tunneling techniques, they erase data by lowering the number of electrons at specific locations in the device structure to the lowest possible value. Then they encode new data by increasing the number of electrons located at a given location up to an exact value.

This complex approach makes possible a highly dense chip structure that offers many parameters – meaning programmable variables that can exist in a large number of different states and offer many shadings of behavior. It is this structural density that allows greater computing capability for a given degree of physical size and power input.

“Our FPAA chip has roughly half a million of these programmable parameters,” Hasler said. “They can be used as a switch in a digital manner – using the lowest possible value for ‘off’ or the highest possible value for ‘on’ – or we can achieve even more rich behavior using intermediate values.”

A New Toolset

The FPAA device includes a small amount of built-in digital circuitry that supports communication within the chip and also helps run the programming infrastructure. Utilizing these support features, the team has developed an extensive set of high-level programming tools to take advantage of the new chip.

Among other things, the new toolset is designed to make working with analog arrays accessible to those familiar with digital designs like FPGAs, which are programmed using comparable high-level tools. The new toolset can both simulate and program the FPAA reconfigurable device. A paper detailing these high-level tools has been published online.

“Our toolset uses high-level software developed in the Scilab/Xcos open-source programs, with an analog and mixed-signal library of components,” Hasler said. “Georgia Tech undergraduates are already using these tools in classes in the School of Electrical and Computer Engineering that cover mixed-signal and analog devices and tools.”

One area in which the analog approach is notably powerful involves command words – voice recognition technology used in devices like smartphones to do such things as wake up circuits from an off state, Hasler said. Like traditional analog sensing circuits, an FPAA offers excellent context-aware capability at extremely low power states.

Hasler said that she has talked with several companies about potential applications of the FPAA in commercial devices. A significant number of FPAA chips has already been produced, but plans for potential large-scale manufacture of the chips have not been finalized. The key technologies in the FPAA system-on-chip are patent pending.

“We believe that analog technology offers very powerful ways to look at physical computing, with considerable potential for commercial, neuromorphic, military and other applications,” Hasler said.

CITATIONS:

Sihwan Kim, et al., “Integrated Floating-Gate Programming Environment for System-Level ICs,” (IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015). http://dx.doi.org/10.1109/TVLSI.2015.2504118

Suma George, et at., “A Programmable and Configurable Mixed-Mode FPAA SoC,” (IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016). http://www.dx.doi.org/10.1109/TVLSI.2015.2504119

Michelle Collins, et al., “An Open-Source Tool Set Enabling Analog-Digital-Software Co-Design,” (Journal of Low-Power Electronics and Applications, 2016). http://dx.doi.org/10.3390/jlpea6010003

Research News

Georgia Institute of Technology

177 North Avenue

Atlanta, Georgia 30332-0181 USA

Media Relations Contact: John Toon (404-894-6986) (jtoon@gatech.edu).

Writer: Rick Robinson

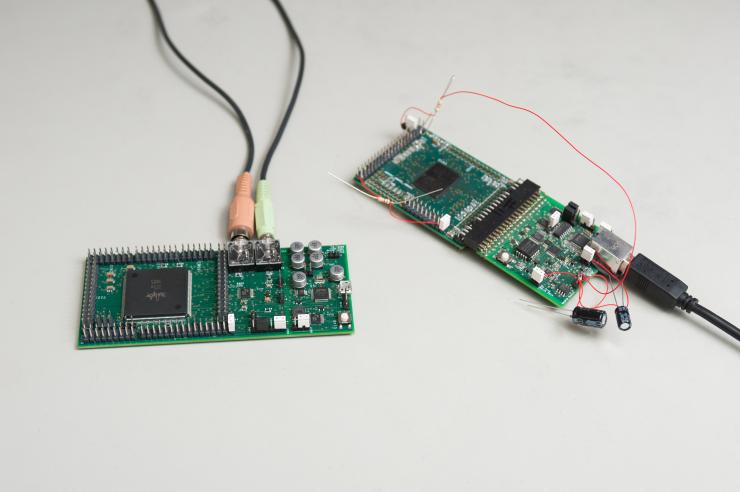

Examples of FPAA chips and printed circuit boards. (Credit: Fitrah Hamid, Georgia Tech)

Georgia Tech Graduate Research Assistant Sihwan Kim and Professor Jennifer Hasler are shown testing FPAA devices at a lab bench. (Credit: Fitrah Hamid, Georgia Tech)

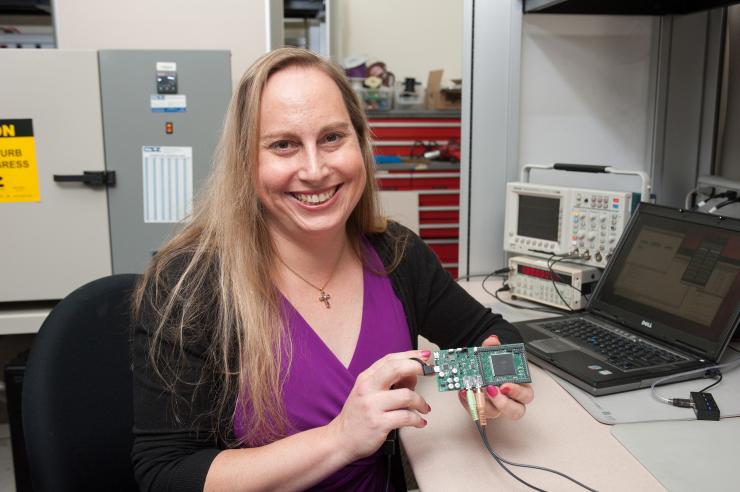

Georgia Tech Professor Jennifer Hasler holding one of the FPAA devices. (Credit: Fitrah Hamid, Georgia Tech)