CRNCH Hosts Neuromorphic Workshop

May 03, 2018 — Atlanta, GA

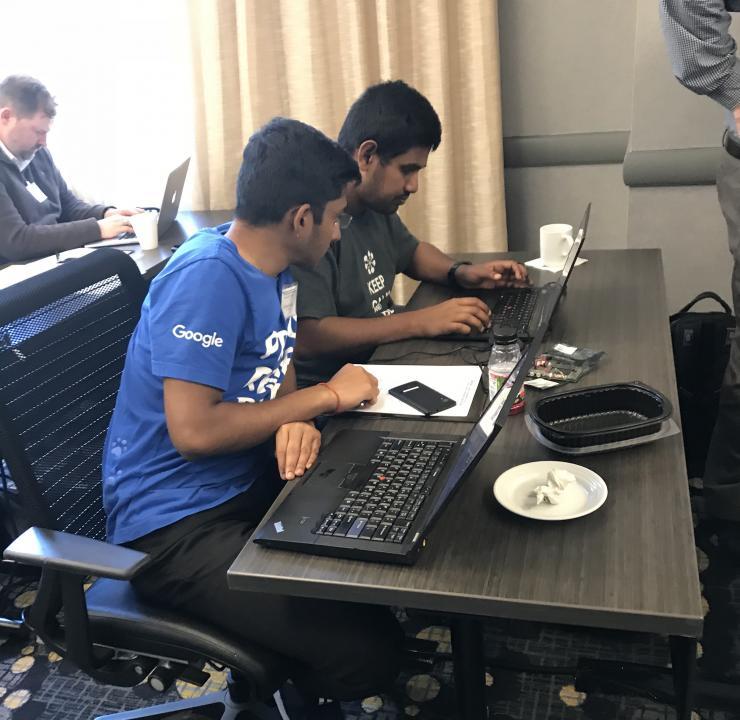

Two dozen people had a unique opportunity to experiment with Georgia Tech–developed hardware that can be used for neuromorphic algorithms on April 27. The training session was part of the Center for Research into Novel Computing Hierarchies’ (CRNCH) first Neuromorphic Workshop.

The all-day event featured overview talks and hands-on sessions with this novel hardware, known as field-programmable analog arrays (FPAA). It was led by School of Electrical and Computer Engineering and CRNCH Professor Jennifer Hasler. Several local and industry participants also presented short talks on their research into neuromorphic computing and current challenges in the area.

An FPAA is a configurable chip that uses analog and digital logic to implement algorithms, drastically reducing the power and size of the chip. For certain applications like neuromorphic computing, analog requires fewer transistors to do the same amount of work as digital and produces fewer errors. While analog computing is traditionally a challenging field for computer scientists, hardware like the FPAA and associated high-level and open-source toolsets developed by Hasler’s group allow researchers to create new analog-based algorithms.

“A single programmable and configurable analog chip can compute a large number of things,” Hasler said.

Providing new avenues for computing performance

Neuromorphic computers replicate the brain in structure, meaning they are highly parallel, run at lower power, and the fundamental unit computation is very small. The low-power nature of FPAAs makes them ideal for neuromorphic computing. Analog and digital hardware like the FPAA could be pivotal to providing new avenues for computing performance in the post-Moore’s law era, in which the number of transistors on an integrated circuit are no longer expected to double roughly every two years as they have for the past half-century.

“Interesting, novel hardware may be able to solve this post-Moore problem,” said Jeff Young, a research scientist in the School of Computer Science and organizer of the workshop.

The workshop gathered Tech students as well as researchers from prominent national labs such as Sandia, Oak Ridge, Lawrence Livermore, and Pacific Northwest National Laboratory. The speakers’ short research talks expanded on how neuromorphic computing will evolve to tackle post-Moore challenges, including:

- Catherine Schumann, Oak Ridge National Laboratory, Evolutionary optimization (EO) training for neuromorphic systems

- Fred Rothganger, Sandia National Laboratories, N2A: A computational tool for modeling from neurons to algorithms

- Constantine Dovrolis, SCS professor, From the Spatio-Temporal Organization of the Brain to Adaptive and Safe Lifelong Learning Machines

- Antonino Tumeo, Pacific Northwest National Laboratory, Exploring the intersection of graph analytics and machine learning

As a follow-up to the workshop, the FPAA will be added to the Rogues Gallery, CRNCH’s collection of obscure and unique hardware. CRNCH provides researchers from around the world access to these machines as part of its strategic goal of rethinking high performance computing. When the gallery launched in fall 2017, it had one specialized type of hardware, the Emu Chick, but has since grown to include field-programmable gate arrays (FPGAs), 3D stacked memory devices, and now the FPAA.

Tess Malone, Communications Officer