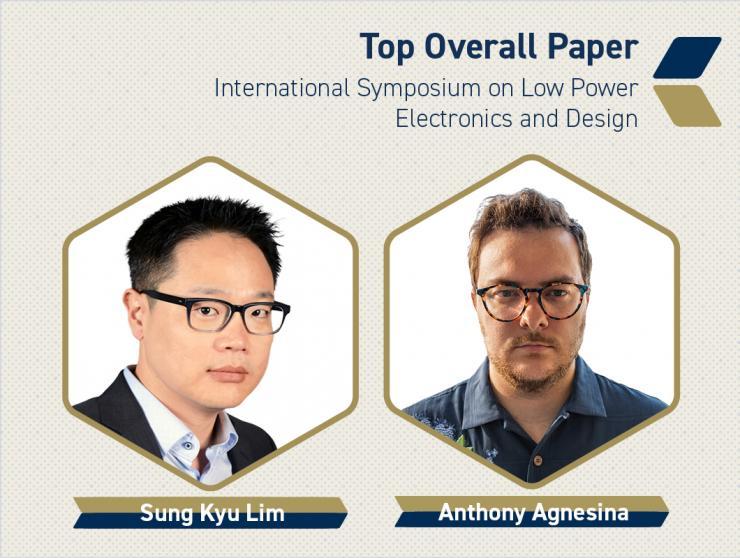

Top Prize Awarded to Lim, Agnesina for 3D IC Design Methodology Research

Aug 11, 2022 — Atlanta, GA

Georgia Tech professor Sung Kyu Lim and recent Ph.D. graduate Anthony Agnesina

The award-winning article proposes a novel hierarchical physical design flow enabling the building of high-density and commercial-quality two-tier face-to-face-bonded hierarchical 3D ICs.

Georgia Tech professor Sung Kyu Lim and recent Ph.D. graduate Anthony Agnesina have won the top paper award at the 2022 International Symposium on Low Power Electronics and Design (ISLPED) for their research entitled, “Hier-3D: A Hier archical Physical Design Methodology for Face-to-Face-Bonded 3D ICs.”

Lim is a Motorola Solutions Foundation Professor in Tech’s School of Electrical and Computer Engineering (ECE) and Agnesina is currently a research scientist at NVIDIA and was advised by Lim while at Georgia Tech. Co-authors include eight researchers from the Interuniversity Microelectronics Centre (IMEC), the University of Bremen, ETH Zurich, and the University of Bologna.

The award-winning article proposes a novel hierarchical physical design flow enabling the building of high-density and commercial-quality two-tier face-to-face-bonded hierarchical 3D ICs. Hierarchical very-large-scale integration (VLSI) flows are an understudied yet critical approach to achieving design closure at giga-scale complexity and gigahertz frequency targets.

The authors significantly reduced the associated manufacturing cost compared to existing 3D IC implementation flows and, for the first time, achieved cost competitiveness against the 2D reference in large modern designs.

Experimental results on complex industrial and open manycore processors demonstrate in two advanced nodes that the proposed flow provides major power, performance, and area/cost (PPAC) improvements of 1.2 to 2.2× compared with commercial 2D ICs, where all metrics are improved simultaneously, including up to 20% power savings.

ISLPED was held at the Boston University Electrical and Computer Engineering Department / Photonics Center on August 1-2, 2022. The symposium is the premier forum for presentation of innovative research in all aspects of low power electronics and design, ranging from process technologies and analog/digital circuits, simulation and synthesis tools, system-level design, and optimization, to system software and applications.

Dan Watson

dwatson@ece.gatech.edu